# Homework 3

(Due date: November 2<sup>nd</sup> @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

## PROBLEM 1 (17 PTS)

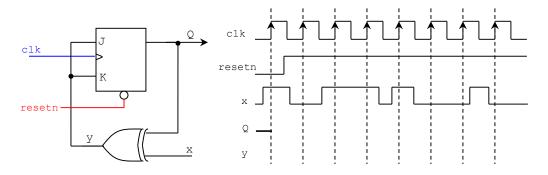

• Complete the timing diagram of the circuit shown below. (5 pts)

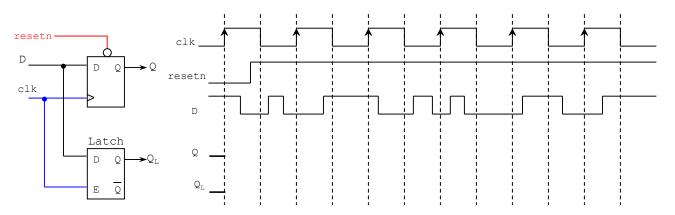

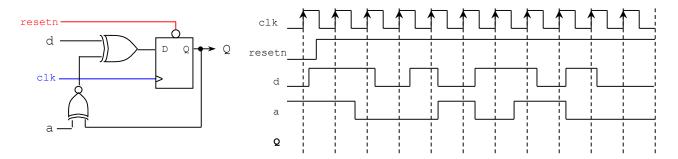

• Complete the timing diagram for the flip flop and the latch shown below: (7 pts)

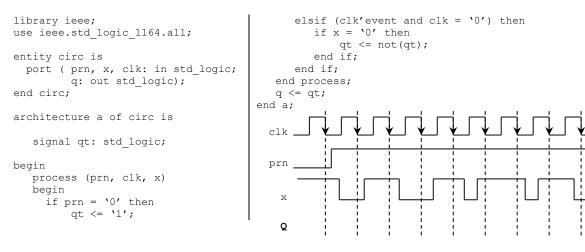

• Complete the timing diagram of the circuit whose VHDL description is shown below: (5 pts)

## PROBLEM 2 (35 PTS)

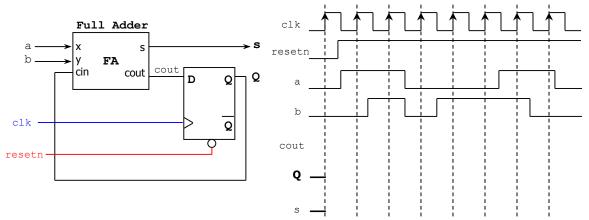

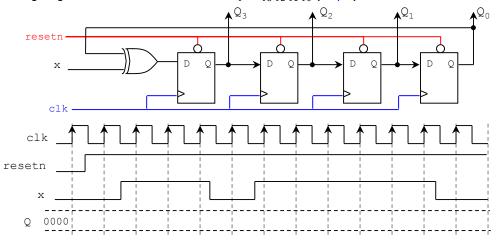

• Complete the timing diagram of the circuit shown below: (10 pts)

• Complete the timing diagram of the circuits shown below: (15 pts)

• Complete the timing diagram of the circuit shown below.  $Q = Q_3 Q_2 Q_1 Q_0$  (10 pts)

2

#### PROBLEM 3 (18 PTS)

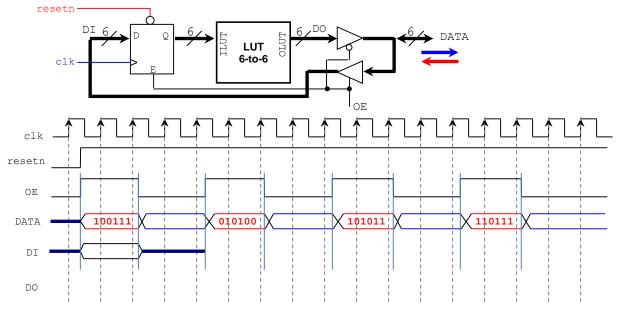

• Given the following circuit, complete the timing diagram (signals *DO* and *DATA*). The LUT 6-to-6 implements the following function: OLUT = [sqrt(ILUT)], where *ILUT* is a 6-bit unsigned number. For example *ILUT* = 35 (100011<sub>2</sub>)  $\rightarrow OLUT = [sqrt(35)] = 6$  (000110<sub>2</sub>)

### PROBLEM 4 (30 PTS)

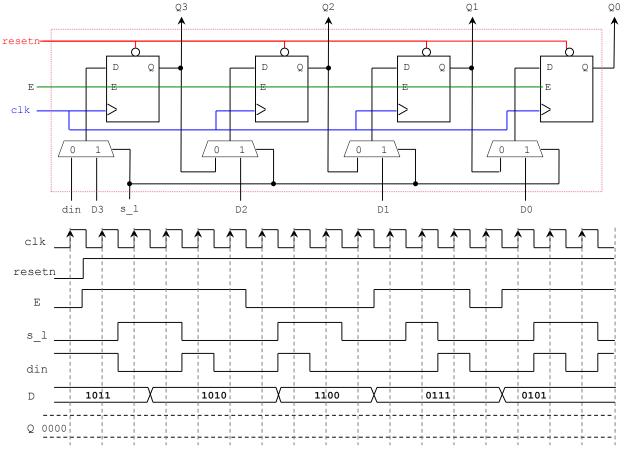

The following circuit is a 4-bit parallel/serial load shift register with enable input.

- Shifting operation:  $s_1=0$ . Parallel load:  $s_1=1$ . Note that  $Q = Q_3Q_2Q_1Q_0$ .  $D = D_3D_2D_1D_0$

- ✓ Write a structural VHDL code. You MUST create a file for: i) flip flop, ii) MUX 2-to-1, and iii) top file (where you will interconnect the flip flops and MUXes). Provide a printout. (10 pts)

- ✓ Write a VHDL testbench according to the timing diagram shown below. Complete the timing diagram by simulating your circuit (Behavioral Simulation). The clock frequency must be 50 MHz with 50% duty cycle. Provide a printout. (20 pts)